Journal of Engineering Research and Reports

19(2): 26-30, 2020; Article no.JERR.62863 ISSN: 2582-2926

# Wirebond Process Optimization through Stitch Relocation on QFN Package

A. Moreno<sup>1\*</sup>, E. Graycochea Jr.<sup>1</sup> and F. R. Gomez<sup>1</sup>

<sup>1</sup>New Product Development & Introduction, STMicroelectronics, Inc., Calamba City, Laguna, Philippines.

Authors' contributions

This work was carried out in collaboration amongst the authors. All authors read, reviewed and approved the final manuscript.

#### Article Information

DOI: 10.9734/JERR/2020/v19i217228 <u>Editor(s):</u> (1) Dr. Y. Thiagarajan, Sri Venkateshwaraa College of Engineering and Technology, India. <u>Reviewers:</u> (1) Rehab Sattar Motlag Alyousuf, Ministry of Higher Education and Scientific Research, Iraq. (2) Anan Sukantharat, UTAC Thai Limited company, Thailand. Complete Peer review History: <u>http://www.sdiarticle4.com/review-history/62863</u>

**Original Research Article**

Received 10 September 2020 Accepted 17 November 2020 Published 02 December 2020

# ABSTRACT

One of the most challenging assembly manufacturing process in semiconductor industry is wirebond process using a wire as direct material. With this new technology, some issues were encountered during the first trial of a quad flat no-leads (QFN) package. This paper is focused on the heal crack seen on the stitch formation during second bond. A comprehensive improvement was done by relocating the stitch formation on the second bond. Ultimately, heal crack occurrence was successfully eliminated.

Keywords: Heal crack; leadframe; QFN; stitch formation; wirebonding.

# **1. INTRODUCTION**

Quad flat no-leads (QFN) leadframe packaging technologies are continuously developed and improved to deliver high quality and robust products for various applications. A common direction of semiconductor manufacturing companies is to increase the production yields and maintain high quality while minimizing the wastage and assembly rejections. Wirebonding process is one of the challenging process in semiconductor industry for integrated circuit (IC) assembly, responsible for attaching the wires to provide electrical connections through combination of heat, pressure and thermosonic energy.

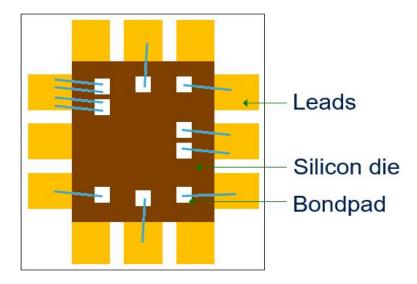

With the new wirebonding layout with four stitches on one lead, a big challenge exists to run the lot or to process this type of technology especially in wirebonding process. The paper presents a solution to successfully process this type of technology in IC assembly manufacturing by relocating the second bond or the stitch formation on the leads. To guarantee its integrity during production run, wirebond process is incorporated with a multiple of criteria such as ball size, ball height, ball aspect ratio, wire pull test, ball shear test, stitch pull test, loop height, intermetallic coverage, and contact angle. The wirebond criteria is performed after machine conversion or setup to ensure that the product is reliable when subjected to reliability tests. Fig. 1 shows the actual reject unit while Fig. 2 gives a representation of a wirebonded unit.

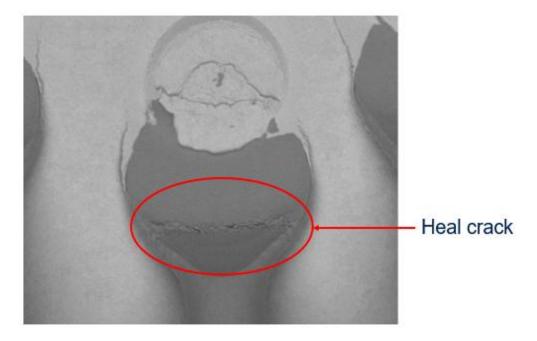

Fig. 1. Actual reject unit with heal crack

Fig. 2. Wirebonding layout

#### 2. PROBLEM IDENTIFICATION

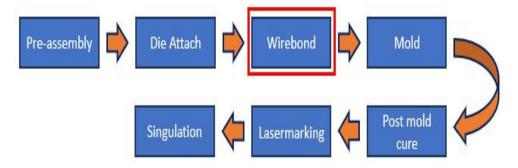

An assembly process flow overview for chip-onlead QFN device from pre-assembly to singulation is illustrated in Fig. 3. Highlighted is the process mostly affected with the concerned issue. Important to note that assembly manufacturing process flow differs with the technology and hence the product [1-3]. With continuing technology development and breakthroughs, challenges in assembly manufacturing are unavoidable [4-7].

Heal crack, as shown in Fig. 1, is the top major assembly reject during the attachment of wires especially on the second bond process, and this was seen during the lot processing phase of the package at wirebonding process station. The heal crack issue is caused by a micro-bouncing effect during the attachment of second bond on the landing area of the leads. Several factors may contribute to the micro-bouncing effect such as the leads not firmly held by vacuum during clamping, non-planarity of the leads, or failing wire clamp and top plate tooling [8-9]. The device in focus used copper (Cu) wire of 2.5 mil size. During wirebonding process of the device, relocation of stitch was employed and comprehensively characterized to address the issue of heal crack occurrence. In the end, the major challenge and motivation is to process the qualification lot with speed without compromising the quality for our customers.

# 3. METHODS AND RESULTS

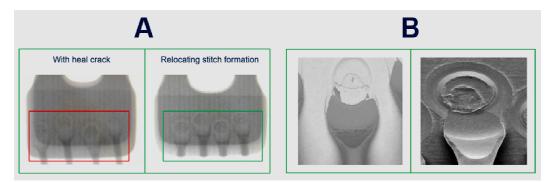

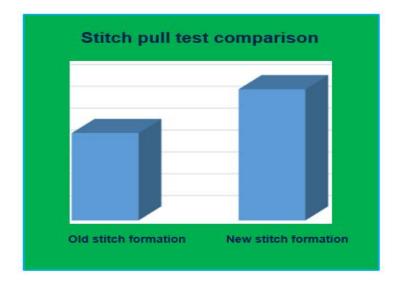

With the intensive process characterization and optimization for the chip-on-lead QFN package, the issue of heal crack in wirebonding process was eventually mitigated. The improved and enhanced process solution was formulated by relocating the stitch formation from the unstable or weak portion of the leads to the stable landing pad as shown in Fig. 4a. Fig. 4b shows the high magnification photo using scanning electron microscope (SEM) of the actual stitch formation. To identify the location of stitch location on the leads, X-ray machine is used to identify if the stitch is at the unstable portion or at the solid landing area. With this solution, the heal crack reject occurrence is effectively eliminated. Another advantage of relocating the stitch formation is the higher reading of stitch pull test, implying that the stitch is properly bonded on the leads of the leadframe. Fig. 5 shows the comparison of stitch pull test from old stitch formation to new stitch formation. Actual reading is purposely not given due to confidentiality.

Fig. 3. QFN assembly process flow

Fig. 4. Actual stitch formation

Fig. 5. Stitch pull test reading comparison

#### 4. CONCLUSION AND RECOMMENDA-TIONS

Wirebonding process optimization and improvement was done to address the heal crack defect occurrence during the process. By relocating the stitch formation on the second bond to ensure stable bonding, heal crack occurrence was successfully eliminated. The improved solution could be used on other semiconductor devices with similar configuration.

Works and learnings discussed in [7-11] are helpful to further improve the assembly processes focused on the wirebonding process. Future studies could include improvement in wire pull test, ball shear test and intermetallic coverage. In-depth comparison of the die attach machines in terms of specifications and capabilities. Comparison of existing works and other studies should also be included for added analysis. It is really important that continuous process improvement is in place to sustain the high quality performance of semiconductor products and the assembly manufacturing.

### ACKNOWLEDGEMENT

The authors are greatly thankful the New Product Development & Introduction (NPD-I) team and the Management Team for the solid support.

### **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

# REFERENCES

- 1. Nenni D, McLellan P. Fabless: The transformation of the semiconductor industry. Create Space Independent Publishing Platform, USA; 2014.

- Doering R, Nishi Y. Handbook of semiconductor manufacturing technology. 2<sup>nd</sup> ed., CRC Press, USA; 2007.

- Geng H. Semiconductor manufacturing handbook. 2<sup>nd</sup> Ed., McGraw-Hill Education, USA; 2017.

- Yeap LL. Meeting the assembly challenges in new semiconductor packaging trend. 34th IEEE/CPMT International Electronic Manufacturing Technology Symposium (IEMT), Malaysia. 2010;1-5.

- Tsukada Y, et al. Trend of semiconductor packaging, high density and low cost. Proceedings of the 4<sup>th</sup> International Symposium on Electronic Materials and Packaging. Taiwan. 2002;1-6.

- Saha S. Emerging business trends in the semiconductor industry. Proceedings of PICMET '13: Technology Management in the IT-Driven Services (PICMET). USA. 2013;2744-2748.

- Tan CE, et al. Challenges of ultimate ultrafine pitch process with gold wire & copper wire in QFN packages. 36th International Electronics Manufacturing Technology Conference. Malaysia. 2014;1-5.

- 8. Sumagpang Jr. A, et al. Non-stick on pad defect reduction through clamp and insert design augmentation. Journal of

Engineering Research and Reports. 2020; 12(2):37-45.

- Pulido J, et al. Wirebond process improvement with enhanced stand-off bias wire clamp and top plate. Journal of Engineering Research and Reports. 2020; 9(3):1-4.

- 10. Moreno A, et al. Wire shorting elimination through wirebond process optimization of

semiconductor sensor device. Journal of Engineering Research and Reports. 2020; 13(4):10-14.

11. Lall P, et al. Reliability of copper, gold, silver, and pcc wirebonds subjected to harsh environment. IEEE 68th Electronic Components and Technology Conference (ECTC). USA. 2018;724-734.

© 2020 Moreno et al.; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Peer-review history: The peer review history for this paper can be accessed here: http://www.sdiarticle4.com/review-history/62863